7晶体

一、时钟时钟是提供所有信号的基础,它的重要性就不做过多强调了。时钟的使用一般有三种方式,一种是主时钟,一种是实时时钟,另一种是特

一、时钟

时钟是提供所有信号的基础,它的重要性就不做过多强调了。

时钟的使用一般有三种方式,一种是主时钟,一种是实时时钟,另一种是特殊功能时钟。

提供时钟的常用分立器件一般有两种:1、晶体。2、晶振。我们先来说一下晶体。

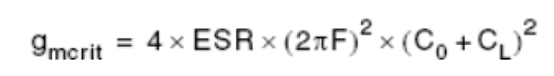

二、晶体的工作原理

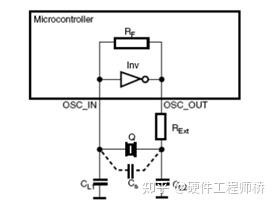

Inv:内部的反向器,作为放大器来工作。

Q:石英晶体或者陶瓷谐振器。

RF:内部反馈电阻(有的器件也需要放置在外部)。

反馈电阻:帮助起振的,一般使用是1M或者10M,具体看CPU手册都会介绍的,或者干脆就集成了,但是我们如果不能确定他是否一定集成了,一定要在外面做一下预留。

RExt:外部电阻,用于限制反向器的输出电流。

CL1 和CL2:两个外部负载电容。

Cs:MCU 引脚( OSC_IN 和OSC_OUT)间和PCB 线路上的杂散电容,它

是一个并联电容

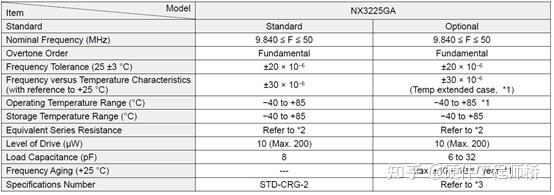

三、晶体的选型:

1、 时钟频率和精度

这个参数一般按照主动器件进行选择就可以。晶体的时钟范围一般在100M以内,多见的就是4M,8M,12M等,实时时钟是32K。

精度,就是是否可以满足对时钟的需求,时钟变化,所有的都要跟着变化。

查看STM32的时钟数说明。20页。也看下AVR 38页

2、 封装

晶体封装都属于标准封装,有两个管脚的,有四个管脚的。四个管脚的其中两个管脚是NC的。晶体也没有方向的。一般封装越小失效率越高,一般超过3225封装以上的都没啥问题,不过这个还是粗略没有经过过多考证的经验,具体根据自己需要进行选择(如果板面积允许,价格合适建议选择大封装)。

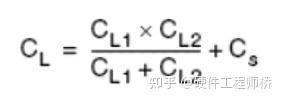

3、 负载电容

负载电容影响晶体的灵敏度和频率等参数,还是非常重要的。CS=5-10pF

计算公式帮助理解负载电容的计算与什么有关,我们选择还是要综合考虑CPU和晶体本身状态,用实际测试波形的方法,将他们调试好。

4、 ESR

ESR如果值比较大会导致晶振无法起振,ESR一般都是越小越好,但是越小也面临着价格越贵。因此应该根据实际情况进行选择。

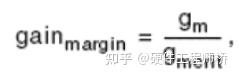

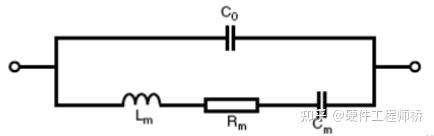

5、增益裕量

增益裕量是一个关键参数,它决定着振荡器是否能够起振。它的表达式是:

● gm 是反向器的跨导(在高频模块中的单位是mA/V ,在32KHz 低频模块中

的单位是μA/V)

● gmcrit(gm 的临界值),取决于晶体的参数。假设CL1 = CL2,并且晶体上的

负载电容与制造商的给定值完全一样,则gmcrit 可用下式来表示:

增益裕量大于5,一般才可以起振。

如果出现不能起振的现象,就要更换晶振,选取一个更低ESR或者负载电容的晶体试一下。

5、 驱动功率

驱动功率就是指晶体内消耗的功率。它必须被限制在一定范围内, 否则晶体

会因过度的机械振动而损坏。最大驱动功率由晶体制造商指定。

超过指定的驱动功率,可能会导致晶体损坏。

如果电流驱动过大,还是需要加入REXT的,串入电阻,分走一部分能量,就会有效的保护晶体,同时还要注意,如果太大,相当于晶体的ESR变大了ESR+REXT,会导致增益裕量变小,无法起振的现象,因此要进行综合考虑

6、 启动时间

晶体的启动时间,与材料,频率,负载电容。ESR都有关系,大家可以根据实际情况进行分析,一般很少要求启动时间。

一个MHz 级的晶体,启动时间一般是ms 级。

32kHz 晶体的启动时间一般在1-5s 范围内。

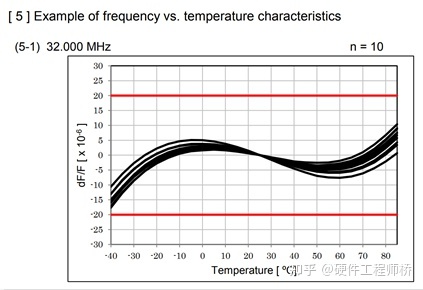

7、 温度特性

注:由于探头上一般存在10~20pF的电容,所以观测时,适当减小在OSCO管脚的电容可以获得更接近实际的振荡波形。工作良好的振荡波形应该是一个漂亮的正弦波,峰峰值应该大于电源电压的70%。若峰峰值小于70%,可适当减小OSCI及OSCO管脚上的外接负载电容。反之,若峰峰值接近电源电压且振荡波形发生畸变,则可适当增加负载电容

四、晶体选型

1、选择晶体首先要根据需要,选择合适的频率、精度、封装。

2、粗略计算一下增益裕量,是否能够满足起振

3、看一下功率是否会超标,如果超标要加入REXT电阻,而且要重新计算增益裕量

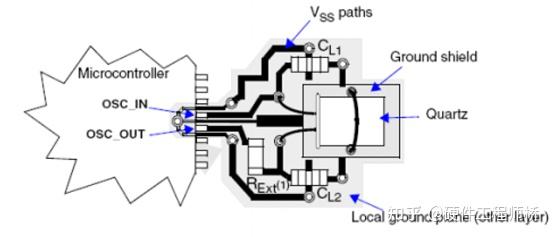

五、晶体PCB的设计

1、走线尽量短

2、有的人晶体下层挖空,这个我没去验证,我一般就是晶体本层下方挖空,下层铺地,相临层不走线。

3、不同的方法,如下图

我一般就是按照前两条进行设计,不做分地,和包地。只要保持和时钟线的距离就可以。上面这种方式我也试过,不过在做EMC实验中,也没有感觉到优化,后来放弃了。大家如果有碰到EMC时钟问题,如果解决不了,可以试试这种PCB的设计方案。

六、常用的电阻厂家

EPSON、NDK